PCB 高速信號測試相關工程師必看 測試題挑戰<基礎篇>

PCB(Printed Circuit Board,印刷電路板)是現代電子產品不可或缺的基礎載體。從伺服器、智慧手機,到電動車和衛星通訊,無處不見 PCB 的身影。

隨著行動通訊與 AI 技術的快速發展,終端產品愈來愈輕薄,資料傳輸速度愈來愈快,對電路板整合能力、高頻高速通訊能力的需求也逐步提升。頻率越高、速率越快,傳輸過程中的信號損耗問題也越嚴重。我們通常利用向量網路分析儀(VNA)對電路板進行介電常數 / 損耗因子(Dk/Df)、信號完整性 SI(阻抗、上升時間、串擾等)、S 參數(回波損耗、插入損耗)等關鍵參數進行測試,以確保信號在電路板中的傳輸可靠性。

無論你是高速信號工程師、射頻工程師,還是硬體設計與量測驗證工程師,掌握 PCB 設計與高速信號測試方法,都是保持競爭力的關鍵。

↓↓↓ 以下高頻高速信號題,快來試試吧 ↓↓↓

<直接挑戰進階篇>

Q1. 高頻高速 PCB 測試所面臨的挑戰主要有哪些面向?

- 高頻信號完整性挑戰

- 在 10 GHz 以上頻段,材料的介電損耗(Df)與導體損耗會導致信號衰減加劇。

- 阻抗允許誤差更嚴苛,需達 ±5% 甚至更低。

- 高密度佈局與差分信號間的電磁耦合引發串擾,影響信號準確性。

- 差分電路設計挑戰

- 差模與共模信號轉換會引入額外損耗與雜訊。

- 差分對之間的時延不一致(Skew)會造成信號失真。

- 材料特性複雜性挑戰

- 材料 Dk/Df 會隨頻率變化,傳統固定模型無法滿足仿真需求。

- 混合材料中玻纖與樹脂分布不均,導致等效 Dk/Df 波動。

- 測試效率與成本壓力

- 開發週期縮短,必須快速完成設計驗證與量產測試。

- 測試集中化成為趨勢,市場要求單一儀表能整合多種測試功能。

Q2.高速PCB信號完整性關鍵參數有哪些?

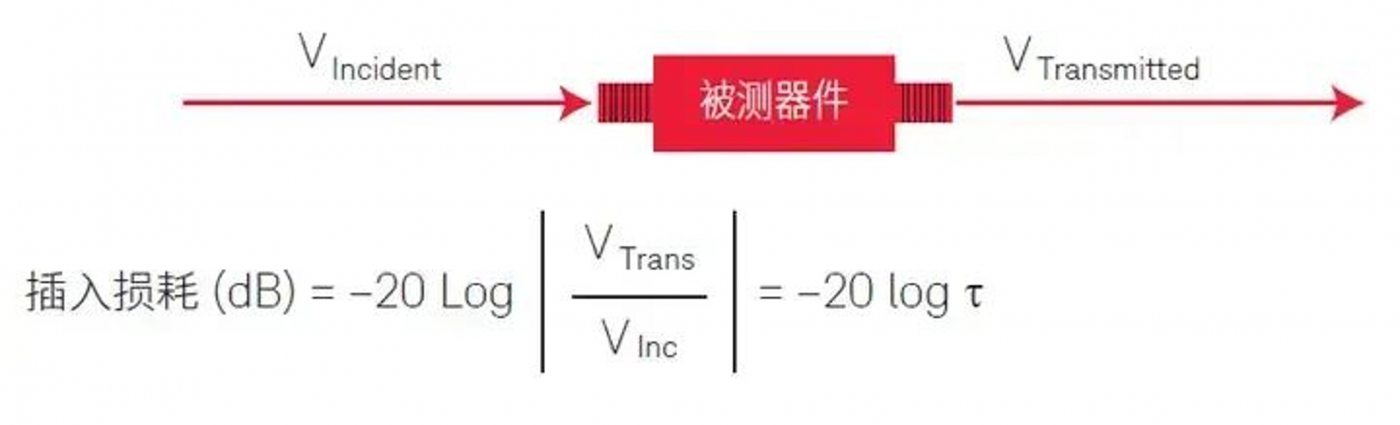

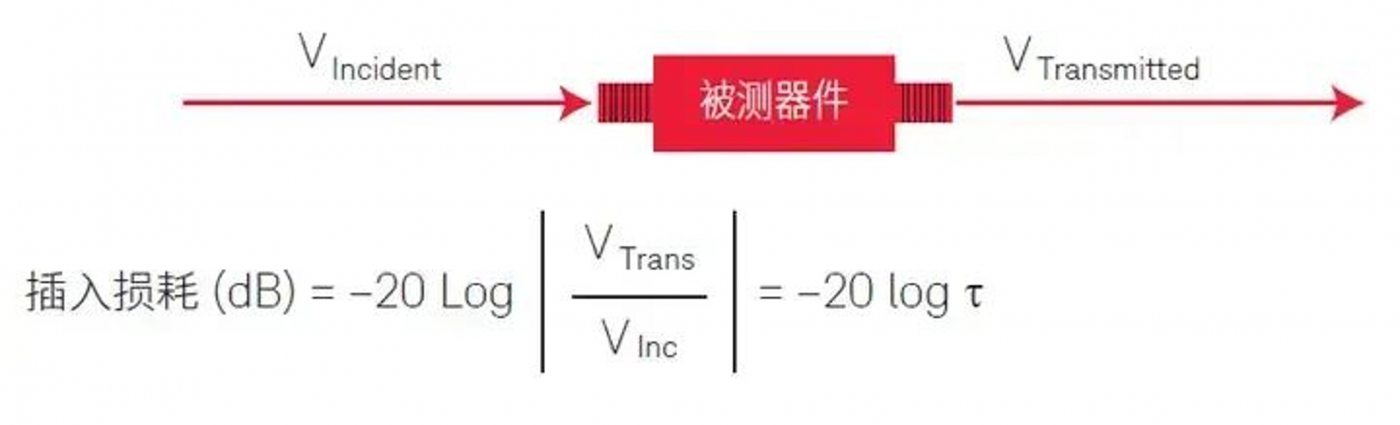

- 插入損耗 (Insertion Loss, IL)

- 插入損耗是指信號從發射端傳輸到接收端時,由電纜、PCB或元件引起的信號衰減,通常以 S21 參數表示。簡單理解為信號在傳輸路徑中的功率損耗,單位為 dB,且通常隨頻率增加而增加。

- 測試方法:使用向量網絡分析儀 (VNA) 測量 S21(正向)或 S12(反向)。測試前需校準設備 (SOLT 或 TRL),並排除連接器或探針的額外損耗。

- 工程實務:IL 對高速差分線影響明顯,對設計信號衰減預算與 PCB 材料選型至關重要。

- 回波損耗 (Return Loss, RL)

- 回波損耗是由阻抗不匹配引起的信號反射,表徵反射信號功率與輸入信號功率的比值。以 dB 表示,反射越小,RL 值越大,信號匹配越好。

回波損耗=−20log(ρ),ρ=∣Γ∣

- 測試方法:使用 VNA 測量 S 參數中的 S11(輸入端口反射)或 S22(輸出端口反射)。

- 工程實務:良好的 RL 可降低信號反射與干擾,對高速接口如 PCIe、DDR 或 SerDes 系統尤為重要。

- 近端串擾 (NEXT, Near-End Crosstalk) 與遠端串擾 (FEXT, Far-End Crosstalk)

- NEXT:發送端附近的鄰線耦合干擾,由鄰近信號線的電磁場引起。

FEXT:接收端附近的鄰線耦合干擾,由發送端信號沿鄰線傳輸後在遠端產生。

- 測試方法:使用 VNA 測量對應端口的串擾電壓。NEXT 測量靠近發射端,FEXT 測量靠近接收端。在訊號傳輸中,近端串擾和遠端串擾是兩個重要的干擾現象,了解這兩種串擾的概念和區別對於設計和維護高品質的通訊系統至關重要。

- 工程實務:

NEXT 主要影響發送端信號質量,遵循 3W 原則(線距 > 線寬 3 倍)可有效降低。

FEXT 直接影響接收端信號判斷,高速接口中需控制幅值與延遲特性。

- 電源層串擾 (PS-Crosstalk)

- PS-Crosstalk 是電源層噪聲耦合至信號層的干擾,對高速信號完整性造成影響。

- 測試方法:使用 VNA 或高速示波器配合專用電源完整性夾具測量,分析電源噪聲對信號層的耦合。

- 插入損耗變化率 (Insertion Loss Change Rate, ICR)

- ICR 表示插入損耗隨頻率或環境條件的變化率,用以評估 PCB 穩定性。

- 測試方法:基於 VNA 在多頻點測量 IL,計算斜率或標準差。

- 插入損耗噪聲 (Insertion Loss Noise)

- IL 噪聲是插入損耗中的隨機波動成分,反映信號傳輸的穩定性。

- 測試方法: 多次測量 IL,分析標準差或噪聲頻譜。

- 差分對延時 (Differential Pair Delay, Skew)

- 高速差分信號線中,兩條線之間或不同差分對之間的傳輸時間差。

Intra-pair Skew:同一對差分線內的單端延時差。

Inter-pair Skew:不同對差分線之間的延時差。

- 測試方法:使用 TDR 或高速示波器測量差分信號的時間差。

- 眼圖 (Eye Diagram)

- 多週期數字信號疊加形成的波形圖,用於評估信號完整性(噪聲、抖動、ISI 等)。

- 測試方法:高速示波器捕獲信號,疊加生成眼圖,可分析眼高、眼寬及抖動。

- 介電常數 (Dk, Dielectric Constant)

- 測試方法:使用諧振腔法、傳輸線法或 VNA 結合微帶/同軸夾具測量 S 參數得到 Dk。

- 介質損耗 (Df, Dissipation Factor)

- 測試方法: 與 Dk 方法相同,通過分析 S 參數或 Q 值計算損耗角正切。

<前往挑戰進階篇>

相關活動

<點擊查看活動詳情>

獲得第一手消息 ! 立即訂閱

獲得第一手消息 ! 立即訂閱